The most recent PuneChips event was easily the most successful one in the short history of the group. Over 50 engineers attended the “SystemVerilog” talk by Clifford Cummings, President of Sunburst Design and SystemVerilog industry guru. A big thank you to a few folks who made this possible is in order; first off Parag Mehta of Qlogic for connecting us with Cliff; secondly in addition to Parag, Pravin Desale and Deepak Lala of LSI, and Jagdish Doma of Virage Logic for driving the attendance. Last, but not the least, we must also thank Cliff for taking us through a complex topic in a very engaging manner. Cliff certainly held the audience in rapt attention through an hour of highly technical discussion. The Q&A session was also very engaging. Of course, Cliff being the industry celebrity that he is, was mobbed by engineers asking questions after his speech.

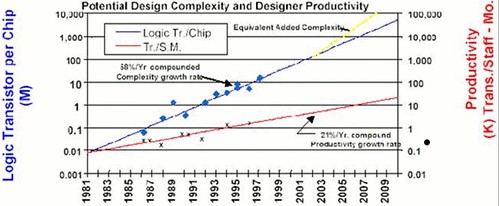

It is very clear that SystemVerilog is clearly targeted at improving designer productivity. Failing productivity due to increasing design complexity is one of the biggest challenges faced by chip designers today, and it is not at all surprising that the EDA tool industry is focused on rectifying this. The chart below (source: SEMATECH) shows a rather grim picture – while design complexity has been growing at 58% CAGR, productivity has been increasing at only 21% CAGR. It is obvious to anyone that tools that fill this gap will be in great demand.

The reason for increasing design complexity is multifold – decreasing geometries allow designers to add more and more elements to the chip, making the entire process challenging. Number of IP cores per chip has grown from ~30 in 2003 to over 250 in 2006 and possibly much more today (source: EETimes). In addition, a big bull’s eye has been painted on power consumption numbers and most chips now must be designed using low power techniques. Plus, increasing complexity means that chip verification becomes more complex; 50% of all ASIC designs today require respins due to functional/logic errors (Source: Colette International Research).

Rather than a single solution, it is very likely that a multitude of innovative solutions that address individual problems will emerge. For example, better modeling techniques that can give a very accurate QoR estimate at the architecture stage itself can reduce the design complexity downstream. Languages such as SystemVerilog literally reduce the lines of code that a designer or verification engineer must write, thus boosting productivity. Time also may be right for ESL design, which has been around for a while, as conventional techniques fail to keep up.

All in all, we live in very interesting times. Faster and smaller is not always for the better. The industry must innovate and rise up to the economic and design challenges if it is to survive and prosper.

Related articles by Zemanta

- PuneChips: Talk by Cliff Cummings on SystemVerilog FSM, Assertion, & RTL tricks for Design Engineers – 5 Nov (punetech.com)

- ASIC Verification: Trends and Challenges (punetech.com)

- Fpga (slideshare.net)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=728924c8-1dbe-416f-bf6b-cdbfb677d6f6)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=6e0578f0-bae0-4d40-9233-274ff3b4f1fb)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=f578279b-a1c0-4bec-8cd2-6229d5905f16)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=f5743e42-43b7-40c7-8c02-50c7534bfd8e)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=5995d7c5-7ba3-4c85-834f-b8ede9420a01)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=5b1426a9-6266-4fb0-80b7-17f5abcc2740)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=2a8c3565-06a7-4e4c-b2eb-c9531b1bb00b)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=a4c21947-3784-4a52-9a7e-294dced5fd90)