Over the past 2 years, PuneTech has covered a breadth of technology related topics, with a concentration on Information Technology & Software. The strategic goal is to cover multiple technology segments and discuss innovative & exciting developments in these areas; specifically in Pune’s context.

It was with this objective that the concept of ‘SIG’ (Special Interest Group) was first mooted last year. A SIG covers a given vertical or horizontal domain area in depth. We decided that the best way to expand PuneTech would be to create a number of such SIGs, each focused on some particular vertical, and each run by someone who is passionate about that vertical. PuneTech would provide support, like a launching pad, publicity and visibility, and guidance about what works and what doesn’t work, based on our own experiences. Over time, we expect SIGs to have their own websites, and their own offline events.

PuneChips was the first SIG, launched in June of 2009, launched by Abhijit Athavale (SIG Leader) in cooperation with PuneTech. It focuses on semiconductors design and applications. This SIG has arranged many successful meetings and events, and now it has also launched has its own website: www.punechips.com . This website features information about the PuneChips events, as well as blogs about the semiconductors and embedded system industry. Volunteers like Arati Halbe have helped with PuneChips (but more volunteers are needed). Also, the Venture Center and Kaushik Gala have been helpful in graciously providing their premises for holding PuneChips events. For more details see the PuneChips about page.

PuneTech hopes to incubate more SIGs like PuneChips in future, and spin them off as separate entities. PuneTech will continue to be actively involved in supporting and publicizing the events and activities of these SIGs. If you’d like to start one, please get in touch with us.

PuneChips Activities

Over the past 8 months, PuneChips has organized a number of interesting meetings, featuring senior thought leaders from the semiconductor industry. It also has an active google-groups mailing list and a ‘Pune Chips’ linkedin group. Nearly 200 professionals and students from the VLSI, Embedded Systems, and other related areas are members of these groups. You can also follow PuneChips on twitter.

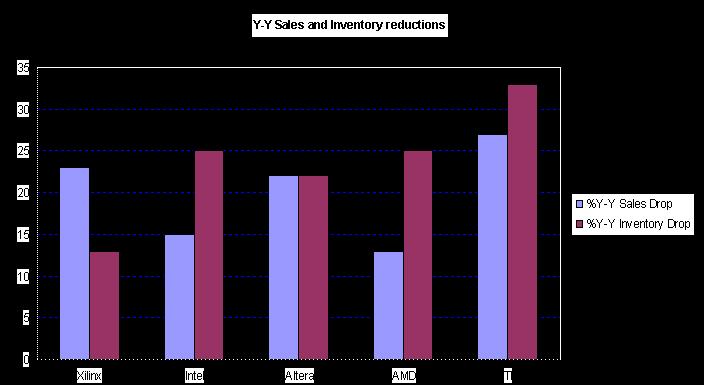

The first kick-off meeting of PuneChips in June 2009 featured Abhijit Abhyankar, Head of Rambus India. His talk on Emerging opportunities in the semiconductor industry presented a nice overview of the semiconductor sector and its progression over the past few decades. He also discussed emerging opportunities and trends in this field.

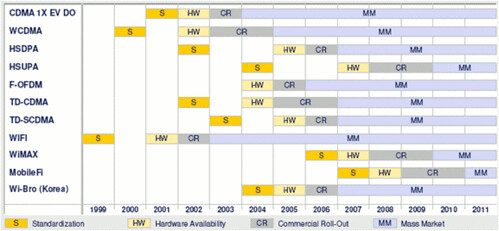

The second event featured Shrinath Keskar, ex-MD of Ikanos India. His presentation: IC Design Challenges in the Telecom sector discussed the various challenges in IC Design, specifically with respect to the Telecom Sector.

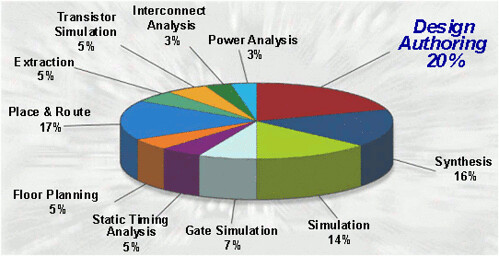

The August 2009 speaker Jagdish Doma, former director of VLSI design Conexant Systems, covered ASIC Verification trends and challenges.

The October 2009 session featured a talk by Cliff Cummings, President of Sunburst Design and SystemVerilog Industry Guru. He talked about SystemVerilog & Designer Productivity, discussing specific tools and tricks for improving designer productivity.

The January session featured Madhu Atre, President of Applied Materials India. His talk on A Bright Solar Future discussed the various new developments in the area of solar power (specifically photo-voltaic) and the macro alternate energy global trends. He also touched upon the implications of these developments for India, including costs and government incentives.

In 2010, PuneChips plans to arrange similar meetings, featuring talks by thought leaders from the industry. The SIG also looks forward to more active interactions on the mailing list and linkedin group. If you are interested in learning more about the PuneChips activities and/or have a speaker you would like to recommend, please contact Abhijit Athavale.

You should form a SIG too – Get in touch with us

It would be great if Pune has many more such SIGs. A number of such groups and organizations are already active (some like the Pune Linux Users Group have existed long before PuneTech was started, and most like the Pune Open Coffee Club, for entrepreneurs and startups, were created independently). But there is scope for many more. The existing ones largely tend to be focused on particular technologies (like the Google Technologies User Group, or the Pune User Group for Microsoft Technologies). There are only a few that are aligned with industry verticals, like PuneChips or the Null group focused on security. I think there should be more.

So, if you’re passionate about some industry vertical, and are willing to spend at least a few hours a week on organizing a Pune-based SIG around that vertical, and are willing to do that for at least a couple of years, please let in touch with us, and let us make it happen.

In fact, it does not even have to be a vertical. It can be a horizontal area that goes across groups. As long as it is something that benefits Pune’s techies, we are game. In fact, we’re soon expecting to make an announcement related to PuneTech and Marathi. Subscribe to PuneTech so you don’t miss it.

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=728924c8-1dbe-416f-bf6b-cdbfb677d6f6)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=d4aa2e75-5a21-458e-9b7e-515596044b58)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=3c345993-e718-4033-9a19-55f231b7a203)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=7742b308-830f-4ef2-8c08-c59af36a6390)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=f4b9ba28-c4dd-46e1-aabe-80e0c4ff48a5)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=6e0578f0-bae0-4d40-9233-274ff3b4f1fb)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=f578279b-a1c0-4bec-8cd2-6229d5905f16)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=dc3f5edb-df18-4b5d-a79a-0655457008e3)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=f5743e42-43b7-40c7-8c02-50c7534bfd8e)