(This post by Abhijit Athavale, the driving force behind PuneTech’s PuneChips forum, is cross-posted from his blog.)

Are we really out of the most dreaded recession after the great depression and on our path to recovery? The answer might be a resounding yes if we look at the recent crop of earnings reports from technology companies, and other data emerging from market analysis firms. In fact, the NASDAQ composite is already into deeply positive territory on the expectations of an imminent recovery.

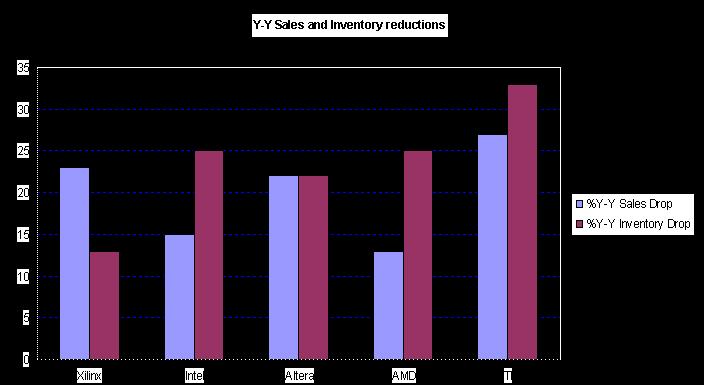

However, a quick dissection of recent earnings announcements from a few prominent semiconductor companies shows that we are not out of the woods yet. The chart above shows that sales numbers are still horribly bad compared to last year, and inventories have declined sharply as well. This means that companies have managed to satisfy the underlying demand by using up their inventories, and will or already have started ordering replacement units from fabs. This explains why the fabs have reported better numbers than the IC vendors. In a normal growth phase, every company wants to keep its channel well stocked to feed demand. This is not the case now as companies are drawing down on finished stock to reduce costs and improve margins. So much for the expected recovery in demand …

Where does this demand come from ultimately? The consumer, of course. The US, Europe (as a whole) and Japan are the three largest economies in the world.

People living in these countries constantly keep (or, at least used to) buying new things such as laptops and PCs, cell phones, gaming consoles, automobiles, audio and video equipment, personal media players, TVs, toys, and other gadgets. Companies that manufacture consumer electronics ICs directly feed this demand. Consumers also buy services such as wireless and wireline voice and data, broadband, cable and satellite TV feeds. This in turn generates demand for the entire telecom, datacom and wireless infrastucture and service providers. Infrastructure IC manufacturers are responsible for suppplying this demand. In the US alone, the consumer is 70% of the entire economy. The consumer is also a major portion of the EU and Japanese economies. The consumption in all three major economies in the world has cratered, as evidenced by the continuous 6 to 9 month declines in the exports from China, Taiwan and Japan, major export reliant countries.

The real demand will not be back till the consumer starts spending again. And, that is almost impossible in this economy. Take the US for example – official unemployment is at ~11% (some say, it is near 16% unofficially), one in ten homeowners is underwater, and credit lines have been severely downgraded by banks. Three major sources of funds used by consumers have been seriously compromised. To use a banking term, the consumer is now de-leveraging and getting his house in order. There will be no more spending sprees till the US savings rates are back to historical levels. The EU and Japan are in even worse situations as their banks are still over leveraged and that still needs to be played out a la Bear Sterns and Lehman Brothers.

My belief is that the semiconductor industry and the companies that serve the semiconductor industry are not coming back till personal finances get better. That is not likely to happen for a while. Some analysts are calling Q2, 2009 as the bottom, which very well may be so, but I don’t expect to see a quick recovery from this point on. In fact, the worsening unemployment and foreclosure numbers may push us back into a double dip recession. If not, the recovery will be tepid and totally unspectacular.

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=6e0578f0-bae0-4d40-9233-274ff3b4f1fb)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=f578279b-a1c0-4bec-8cd2-6229d5905f16)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=dc3f5edb-df18-4b5d-a79a-0655457008e3)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=f5743e42-43b7-40c7-8c02-50c7534bfd8e)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=5995d7c5-7ba3-4c85-834f-b8ede9420a01)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=5b1426a9-6266-4fb0-80b7-17f5abcc2740)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=2a8c3565-06a7-4e4c-b2eb-c9531b1bb00b)

![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=a4c21947-3784-4a52-9a7e-294dced5fd90)

What: Talk by Abhijit Abhyankar, country head of

What: Talk by Abhijit Abhyankar, country head of ![Reblog this post [with Zemanta]](http://img.zemanta.com/reblog_b.png?x-id=063a8619-be3f-4f1b-b33f-903762e27723)